# Educational Tool for the Demonstration of DFT Principles Based on Scan Methodologies

Josef Strnadel and Zdeněk Kotásek Faculty of Information Technology Brno University of Technology

#### Presentation Outline

- Scan Educational Tool (SET)

- Description of particular SET windows

- Scan-layout selection example

- Testability analysis example

- Loop-breaking example

- Test data propagation paths browser example

- Automated DFT process example

- SET requirements and limitations

- Conclusions

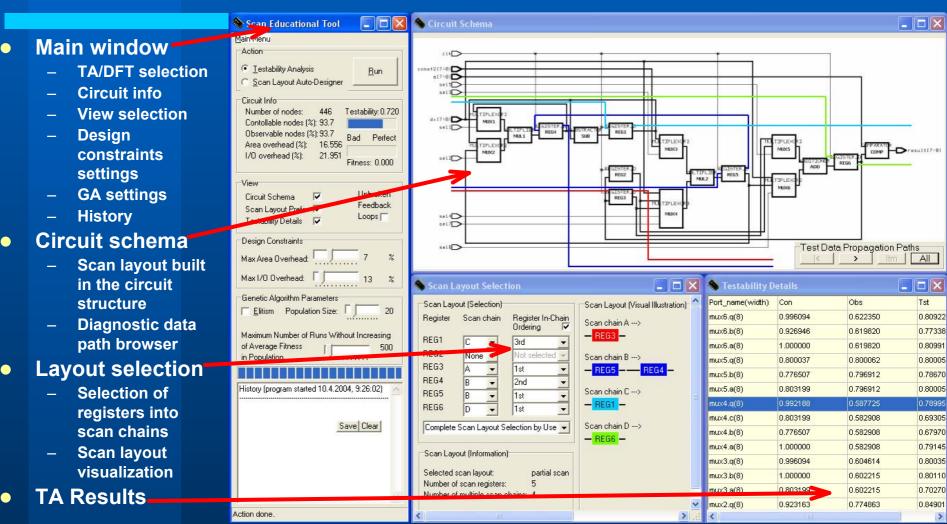

#### Scan Educational Tool (SET)

#### SET: Main window

- Action selection

- Circuit information (valid after action is done)

- Selection of windows to view

- Design constraints (area, I/O) settings

- Genetic algorithm settings

- Elitism

- Population size

- •Max # of runs

- Progress bar

- History (setting+result logging) window

- Status bar (current action info)

#### SET: Circuit schema window

- Educational circuit schema

- Test data propagation paths browser for selected functional unit

- Go to the path-start (primary inputs)

- Perform 1 step towards pathend (primary outputs)

- Write information about test data propagation paths of

- Selected functional unit

- •All functional units into History window

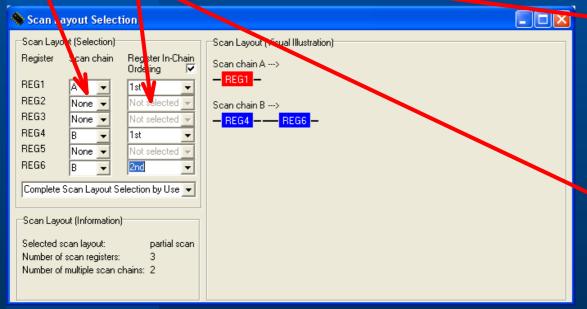

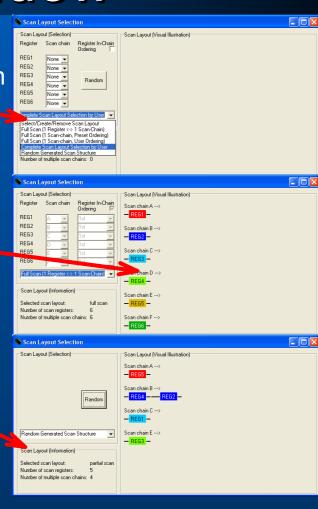

### SET: Scan-layout window

- •User/predefined/random (U/P/R) scan-layout selection

- U/P/R inclusion of registers into scan chains

- V/P/R ordering registers within scan chains

- Selected scan-layout

- Vizualization

- Information

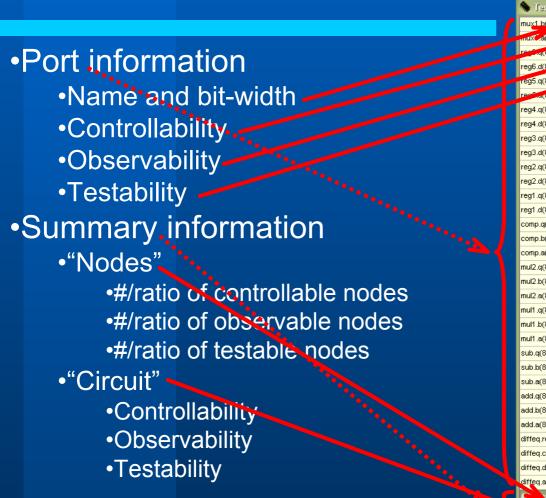

#### SET: Testability results window

Scan-layout selection example

DSD 2005 - 8th Euromicro Conference on Digital System Design, Architectures, Methods and Tools (Porto, Portugal)

# Testability analysis example

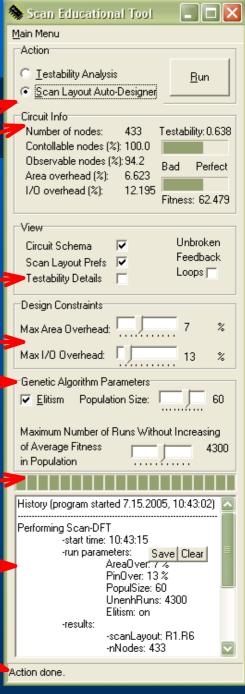

Testability Analysis

Observable nodes (%): 94.2

Area overhead (%): 6.623

Scan Layout Prefs

Testability Details

Testability: 0.520

Unbroken Feedback

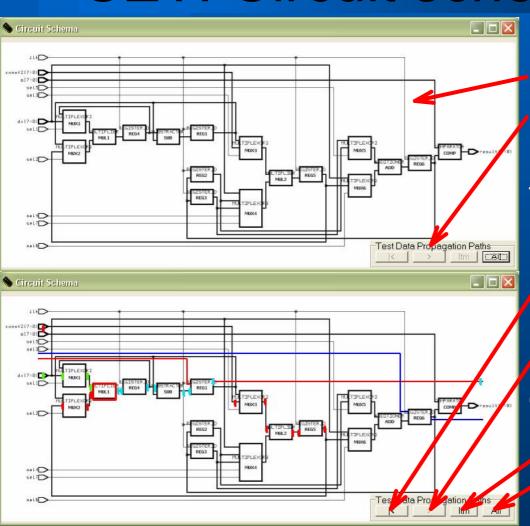

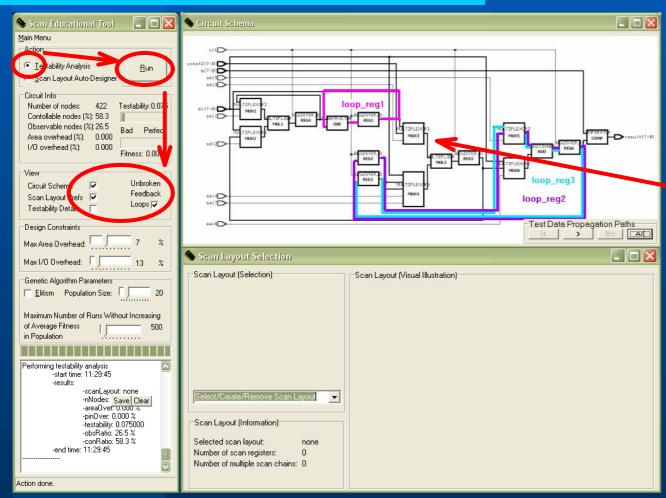

# Loop-breaking example (1)

When no scan-layout is selected

then

all 3 loops remain unbroken

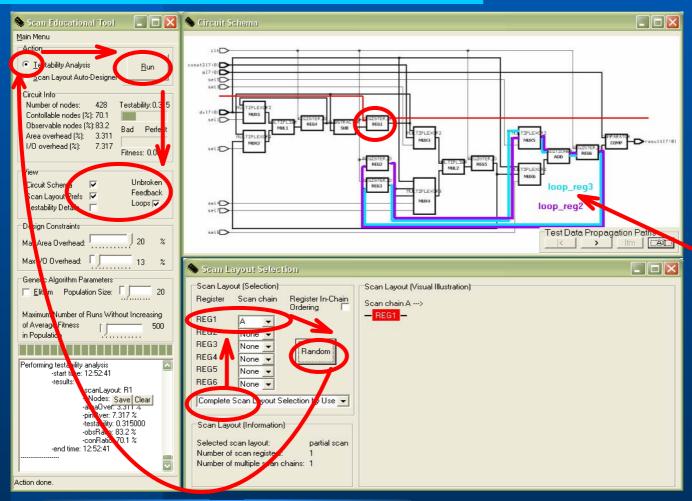

# Loop-breaking example (2)

When REG1 is included into scan chain A

then

2 of 3 loops remain unbroken

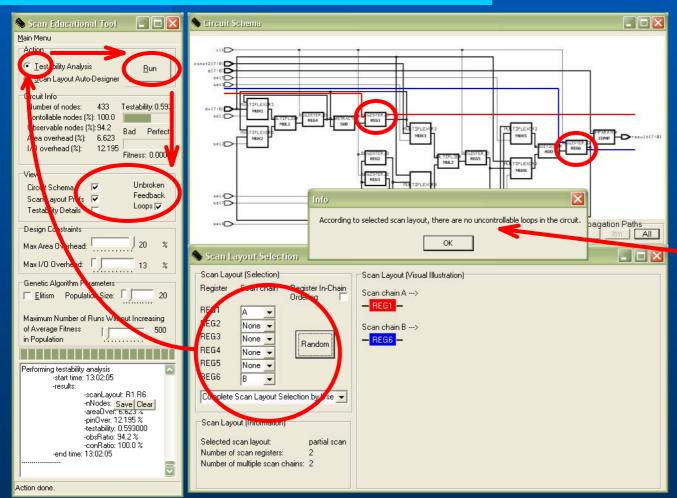

# Loop-breaking example (3)

When REG1, REG6 are included into scan chains

then

all 3 loops become broken

#### Test data propagation paths browser

DSD 2005 - 8th Euromicro Conference on Digital System Design, Architectures, Methods and Tools (Porto, Portugal)

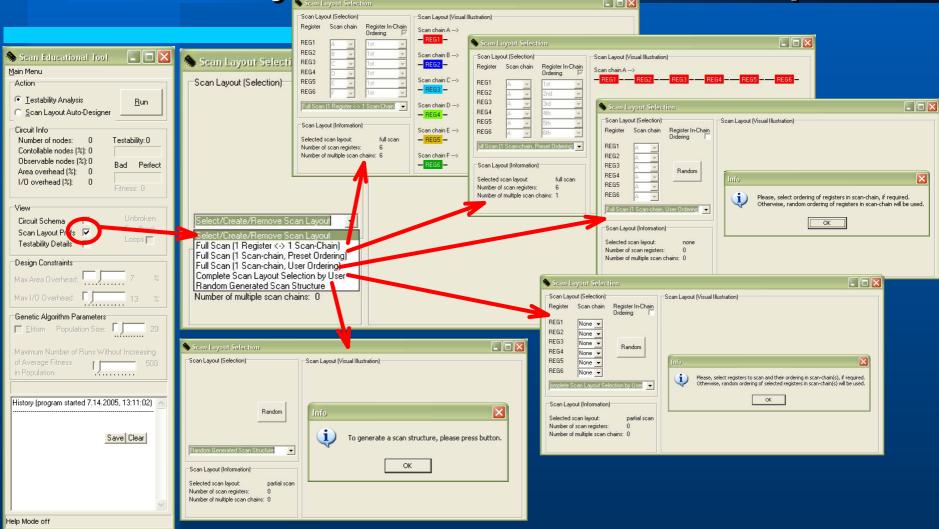

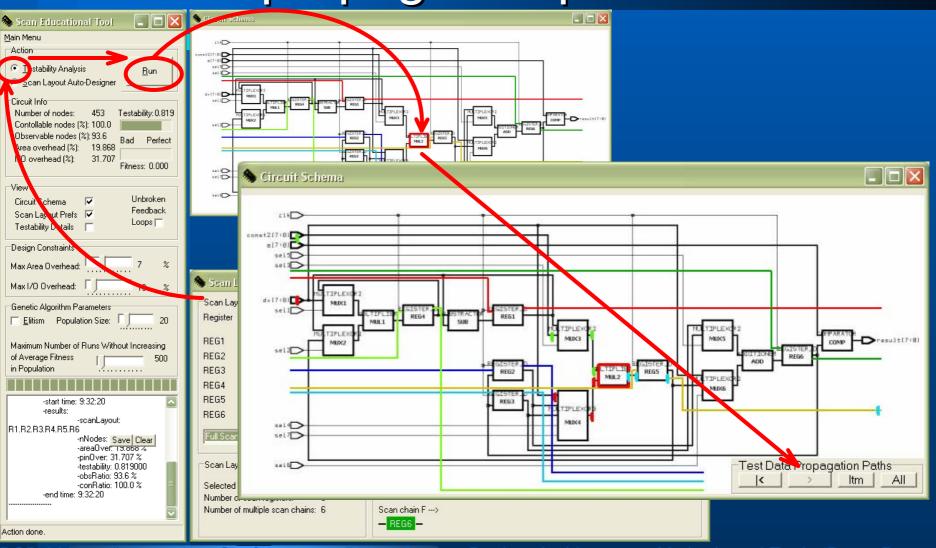

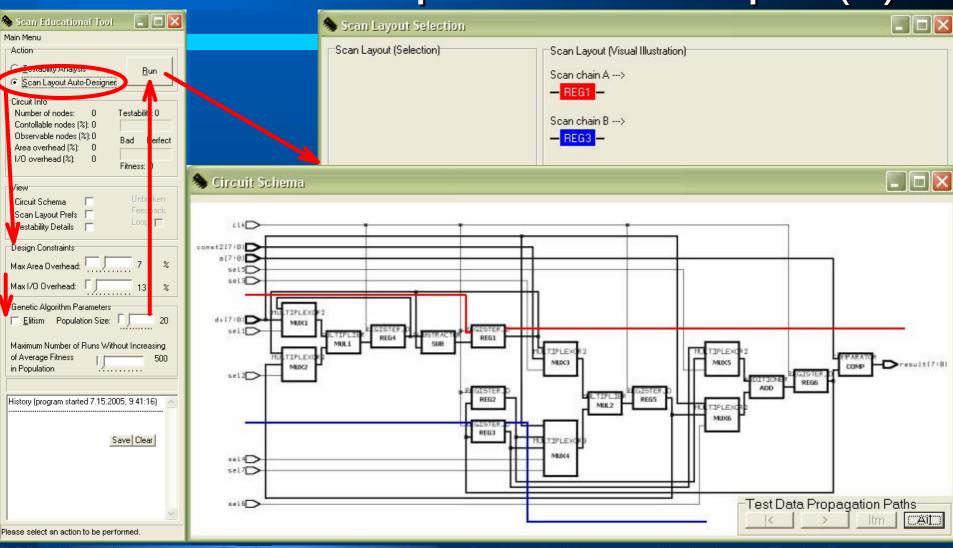

#### Automated DFT process example (1)

DSD 2005 - 8th Euromicro Conference on Digital System Design, Architectures, Methods and Tools (Porto, Portugal)

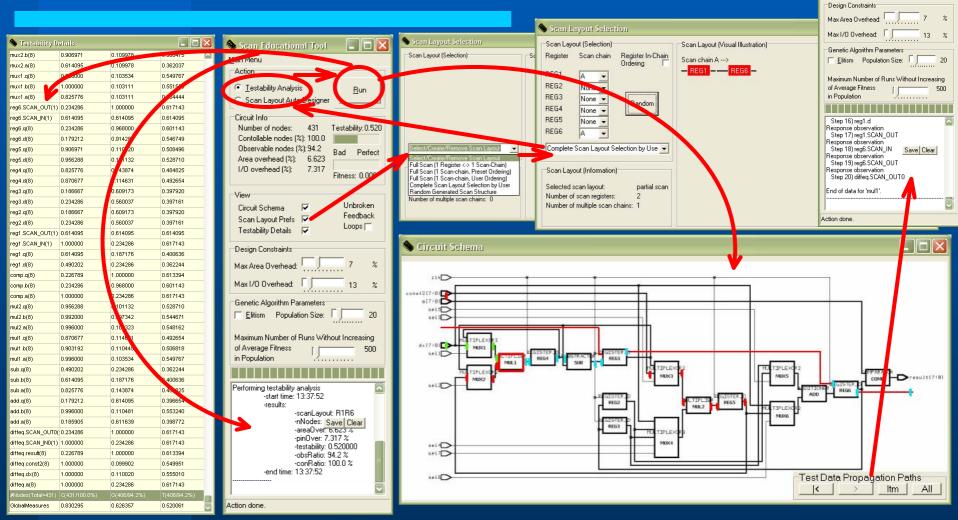

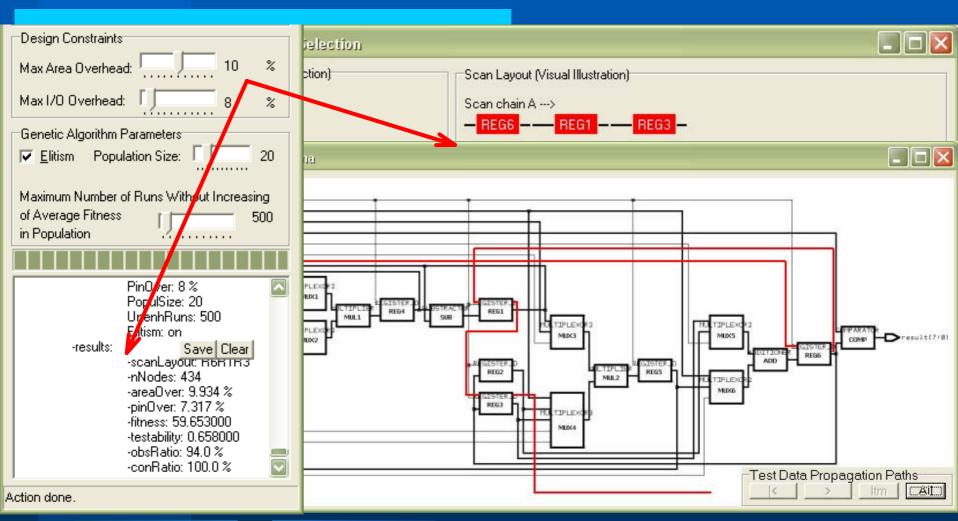

#### Automated DFT process example (2)

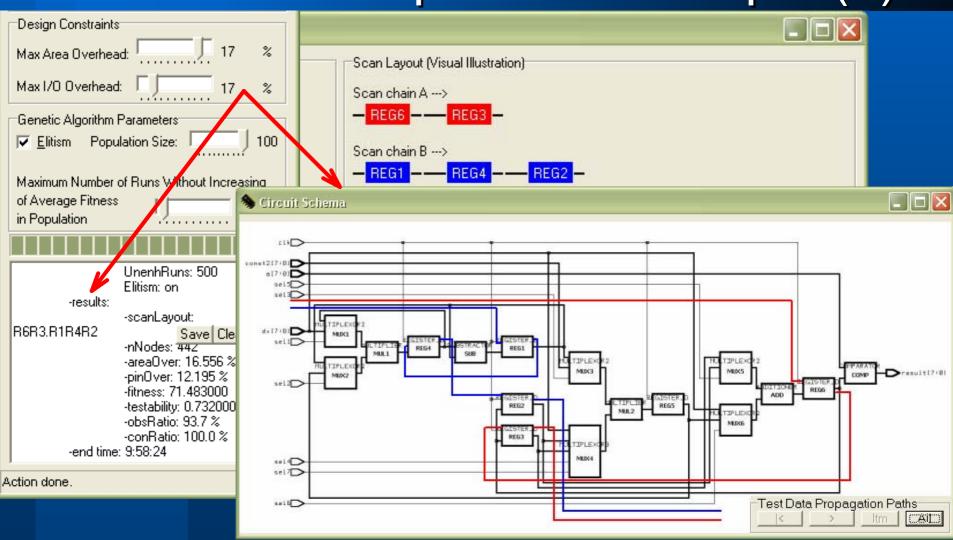

#### Automated DFT process example (3)

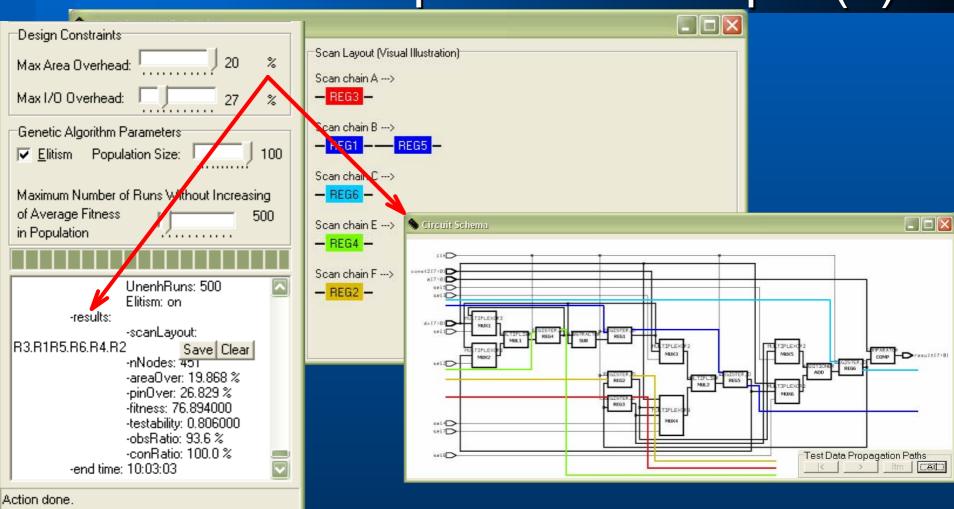

#### Automated DFT process example (4)

## SET requirements and limitations

#### **Actual SET:**

- Requirements

- WIN32 environment to run SET in graphical user interface mode

- Original/emulated MS-DOS environment to run SET in command line mode

- Limitations

- Non-commercial use only (see SET licencing conditions)

- Set of educational circuits is limited to one circuit in the set

#### Conclusions

# Acknowledgements: The research and software development has been financially supported by the

- Grant Agency of the Czech Republic under contracts

- No. 102/04/0737 "Modern methods of digital systems design",

- No. GA102/05/P193 "Optimizing Methods in Digital Systems Diagnosis"

- IST-2000-30193 project REASON.