NetCOPE platform

For handling communication and data transfers between the software and the hardware part we have decided to use the NetCOPE platform. Originally it was intended to be used for rapid network application development, however, it can be used as generic acceleration platform as well. Moreover, because Net- COPE provides a uniform interface over several protocols, its use makes it very easy to change the framework to use Ethernet or other supported communication protocol for data transfers instead of a system bus without any change to the verification environment itself.

NetCOPE platform provides an abstract layer between operating system (software drivers and libraries) and an FPGA (especially DMA transfers between the acceleration cards and the host machine's RAM memory through the PCI Express bus). Thanks to the unified interface of hardware application we can achieve a complete abstraction from underlying physical card with FPGA. NetCOPE platform provides an abstract layer over the whole family of COMBO cards.

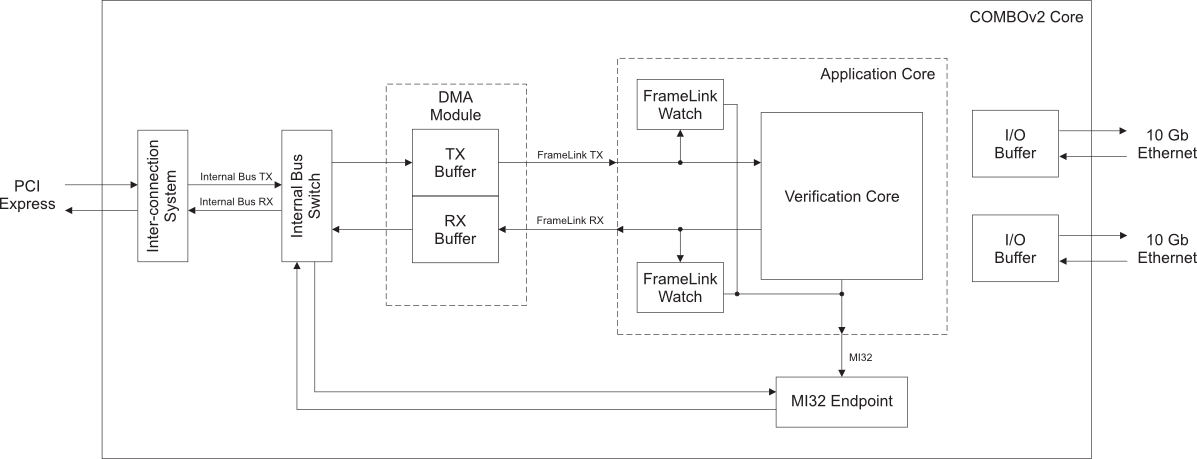

From the NetCOPE package we use especially the layer for communication over PCIe bus and software. For data transfers between DMA buffers and PCIe bus Fast Internal Bus implemented directly in FPGA is used. The architecure of the NetCOPE acceleration card connected with verification core is displayed in following figure:

Transmission of data between the RAM memory and the acceleration card is realized through the ring buffers in NetCOPE. The pair of ringbuffers is located both in FPGA and in system kernel memory space in RAM. For communication with verification core, a FramLink protocol is used. FrameLink is derived from Xilinx LocalLink protocol.

MI32 is a protocol used especially for transfer of control information. Typical usage is for initialization of hardware components, reading and writing control information from or to component's memory. It has been primarily designed for communication with components which map their configuration registers into the memory address space of the acceleration card.

Pair of input and output buffers connected to 10 Gb Ethernet interfaces is not currently used. Nevertheless, acceleration framework can easily be modified to benefit from using the Ethernet interfaces instead of computer's system bus.