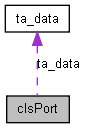

clsPort Class Reference

object of the class represents port within module/circuit/design interface More...

#include <model.h>

Public Member Functions | |

| clsPort (string nm, int nt, int w, bool orig=true) | |

| width based constructor | |

| clsPort (string nm, int nt, int hb, int lb, bool orig=true) | |

| low/high bit based constructor | |

| ~clsPort () | |

| destructor | |

| bool | operator< (clsPort const &c) const |

| definition of the '<' operator over class objects | |

| bool | operator!= (clsPort c) const |

| definition of the '!=' operator over class objects | |

| bool | operator* (clsPort const &c) const |

| definition of the '*' operator over class objects | |

| string | getName () const |

| gets port's name | |

| int | getType () const |

| gets port's type | |

| int | getWidth () const |

| gets port's width | |

| int | getLBit () const |

| gets port's low-bit | |

| int | getHBit () const |

| gets port's high-bit | |

| bool | addBit (int bn, int nt, bool orig=true) |

| adds bit to a port's clsPort::mapBit | |

| bool | addBits (bool orig=true) |

| adds bits within port's width-range to a port's clsPort::mapBit | |

| clsBit * | findBit (int bn) |

| searches for a bit within the port | |

| map< int, clsBit >::iterator | getMapBitBegin () |

| gets begining of port's clsPort::mapBit | |

| map< int, clsBit >::iterator | getMapBitEnd () |

| gets end of port's clsPort::mapBit | |

| t_TAdata | getTAdata () const |

| gets port's testability-mark | |

| void | setTAdata (t_TAdata _ta_data) |

| sets port's testability-mark | |

| void | clrTAdata () |

| clears port's testability-mark | |

| int | getNCon () |

| gets number of controllable bits within the port | |

| int | getNObs () |

| gets number of observable bits within the port | |

| int | getNTst () |

| gets number of testable bits within the port | |

| void | evalTst () |

| evaluates testability of the port | |

| void | setOrig (bool v) |

| sets originality flag of the object to v value | |

| bool | getOrig () const |

| gets value of object's originality flag | |

Data Fields | |

| map< int, clsBit > | mapBit |

| map of all bits within port | |

Private Attributes | |

| string | name |

| port name | |

| int | node_type |

| port type (see enum tNode) | |

| int | lbit |

| low-bit of the port | |

| int | hbit |

| high-bit of the port | |

| bool | orig |

| originality flag. Set to true for a bit originally present in the design | |

| t_TAdata | ta_data |

| testability analysis related data | |

Detailed Description

object of the class represents port within module/circuit/design interfaceinformation about ports related to particular module/circuit/design interface is read from a file whose name must be specified by means of tool's command line parameters (see tool's help to -i command line parameter). Each module/circuit/design is assigned an independent set of the class objects (stored in clsModule::mapPort / clsCircuit::mapPort / clsDesign::mapPort maps).

Constructor & Destructor Documentation

| clsPort::clsPort | ( | string | nm, | |

| int | nt, | |||

| int | w, | |||

| bool | orig = true | |||

| ) |

width based constructor

- Parameters:

-

[in] nm name of the port [in] nt port type (see enum tNode) [in] w port width [in] orig originality flag (implicitly set to true)

| clsPort::clsPort | ( | string | nm, | |

| int | nt, | |||

| int | hb, | |||

| int | lb, | |||

| bool | orig = true | |||

| ) |

low/high bit based constructor

- Parameters:

-

[in] nm name of the port [in] nt port type (see enum tNode) [in] hb high-bit of the port [in] lb low-bit of the port [in] orig originality flag (implicitly set to true)

| clsPort::~clsPort | ( | ) |

destructor

Member Function Documentation

| bool clsPort::operator< | ( | clsPort const & | c | ) | const [inline] |

definition of the '<' operator over class objects

| bool clsPort::operator!= | ( | clsPort | c | ) | const [inline] |

definition of the '!=' operator over class objects

| bool clsPort::operator* | ( | clsPort const & | c | ) | const [inline] |

definition of the '*' operator over class objects

| string clsPort::getName | ( | ) | const [inline] |

gets port's name

| int clsPort::getType | ( | ) | const [inline] |

gets port's type

| int clsPort::getWidth | ( | ) | const [inline] |

gets port's width

| int clsPort::getLBit | ( | ) | const [inline] |

gets port's low-bit

| int clsPort::getHBit | ( | ) | const [inline] |

gets port's high-bit

| bool clsPort::addBit | ( | int | bn, | |

| int | nt, | |||

| bool | orig = true | |||

| ) |

adds bit to a port's clsPort::mapBit

- Parameters:

-

[in] bn number of the bit to be added to port [in] nt type of the bit to be added to port (see tNode) [in] orig originality flag (implicitly set to true)

| bool clsPort::addBits | ( | bool | orig = true |

) | [inline] |

adds bits within port's width-range to a port's clsPort::mapBit

| clsBit* clsPort::findBit | ( | int | bn | ) | [inline] |

searches for a bit within the port

| map<int, clsBit>::iterator clsPort::getMapBitBegin | ( | ) | [inline] |

gets begining of port's clsPort::mapBit

| map<int, clsBit>::iterator clsPort::getMapBitEnd | ( | ) | [inline] |

gets end of port's clsPort::mapBit

| t_TAdata clsPort::getTAdata | ( | ) | const [inline] |

gets port's testability-mark

| void clsPort::setTAdata | ( | t_TAdata | _ta_data | ) | [inline] |

sets port's testability-mark

| void clsPort::clrTAdata | ( | ) | [inline] |

clears port's testability-mark

| int clsPort::getNCon | ( | ) |

gets number of controllable bits within the port

- Warning:

- return value valid only if testability analysis was run before call of the function

| int clsPort::getNObs | ( | ) |

gets number of observable bits within the port

- Warning:

- return value valid only if testability analysis was run before call of the function

| int clsPort::getNTst | ( | ) |

gets number of testable bits within the port

- Warning:

- return value valid only if testability analysis was run before call of the function

| void clsPort::evalTst | ( | ) |

evaluates testability of the port

- Warning:

- return value valid only if testability analysis was run before call of the function

| void clsPort::setOrig | ( | bool | v | ) | [inline] |

sets originality flag of the object to v value

| bool clsPort::getOrig | ( | ) | const [inline] |

gets value of object's originality flag

Field Documentation

string clsPort::name [private] |

port name

int clsPort::node_type [private] |

port type (see enum tNode)

int clsPort::lbit [private] |

low-bit of the port

int clsPort::hbit [private] |

high-bit of the port

bool clsPort::orig [private] |

originality flag. Set to true for a bit originally present in the design

t_TAdata clsPort::ta_data [private] |

testability analysis related data

- Warning:

- value valid only if testability analysis was run before reading the value

| map<int, clsBit> clsPort::mapBit |

map of all bits within port

The documentation for this class was generated from the following files:

1.5.6

1.5.6